Comprehensive List of Researchers "Information Knowledge"

Department of Information Engineering

- Name

- SHIMADA, Hajime

- Group

-

Information Network Systems Group

- Title

- Associate Professor

- Degree

- Doctor of Engineering

- Research Field

- Green Computing / Information Network / Computer Architecture

Current Research

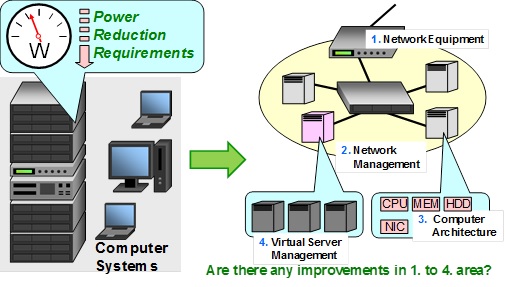

Green Computing via Reducing Power Consumption of Information Infrastructure System

In recent years, even in home appliances accept information through the Internet so that the electric power consumed by servers and network routers are increasing year by year. The power consumption occupation data differs between the statistic scores, but some statistic talks “In average, information related appliances consumes 40% of electric power in companies.” and “The power consumption of the information appliances are separated into 50% of air conditioning, 10% of power conversion, 25% of server machines, and 10% of network appliances.”

It is well taught that the power consumption of those information appliances increase year by year in recent years. But conventional energy source is under competitive in earth scale and it evacuates carbon dioxide so that supply additional power with conventional power plant is unwelcome matter. Nevertheless, the natural power sources which is estimated to increase in later days is comparatively unstable so that it does not adopt to server infrastructures because they consider stability to the first priority.

To alleviate this problem, we have to promote green computing or green IT which aims environmental sensitive technology. It reduces the power consumption of the computer system or operates with fine grained power consumption control to catch up with unstable natural power sources. I’m just eager to promote power reduction side researches. Generally, the power consumption reduction has a trade-off relationship between computer system performance and reliability. So, the typical scenario considers large power reduction by sacrificing small performance or reliability. So, I’m just considering create system with dynamically configurable organization even if it requires some overhead. By catch up with partial workload in fine granularity, we reduce power consumption.

The detail of research topics is as follows.

1. Improving Communication Power Control of Network Appliances

Recent metal wire Ethernet achieves 10Gbps and wireless Ethernet achieves 1.3Gbps, respectively. High speed communication standard achieves low power consumption per 1-bit transfer, but it increases power consumption per fixed time because it enlarges electrical circuit scale. So, even in standards, it includes energy efficiency aimed standards like the Energy Efficient Ethernet which reduces idle power. In my research, I’m promoting application cooperative sleep control to achieve further power consumption reduction.

2. and 4. Network Management Improvement and Virtual Server Management Improvement

In recent years, a network communication becomes an important infrastructure so that a typical network utilizes redundant organization to avoid big failure even if one network path has failed. However, the redundancy is a nothing but a unnecessary power consumption source excluding emergency so that I consider to reduce the power without degrading failure rate. The similar problem also occurs in server area. So, I’m just exploring energy efficient redundancy by sharing spare resources between far area in physical via network management and virtual server management collaboration.

3. Computer Architecture Improvement for Server Machines

As I taught in the beginning, Server Machines consumes 25% of the power consumption. Also, it largely affects power consumption of air conditioning and power conversion so that the power consumption reduction in computer architecture area is important topic since early times. I’m promoting researches which implement power consumption reduction idea into electric circuit of the processor (e.g. dynamic pipeline modification, data migration control between ALUs, dynamic data compression).

Career

- He received D.E. degree from Nagoya University in 2004. He was an COE researcher in Nagoya University in 2004. He was an assistant professor in Kyoto University from 2005 to 2009. He was an associate professor in NAIST from 2009 to 2013. He is now an associate professor in Nagoya University, Japan since 2013.

Academic Societies

- IEEE

- IPISJ

- IEICE

Publications

- R. Kobayashi, D. Matsukawa, Y. Shimomura, H. Ochiai, and H. Shimada, " Reducing Cache Hardware by Focusing on Data Redundancy (in Japanese)," IEEJ, Vol. 133, No. 8, Sec. C, pp. 1597-1606, Aug. 2013.

- J. Yao, K. Ogata, H. Shimada, S. Miwa, H. Nakashima, and S. Tomita, "An Instruction Scheduler for Dynamic ALU Cascading Adoption," IPSJ, Trans. on ACS, Vol. 2, No. 2, pp. 30-47, Jul. 2009.

- H. Shimada, H. Ando, and T. Shimada, "Reducing Processor Energy Consumption with Pipeline Stage unification (in Japanese)," IPSJ, Trans. on ACS, Vol. 45, No. SIG 1 (ACS 4), pp. 18-30, Jan. 2004.